计算机组成 -- 建立数据通路

三种周期

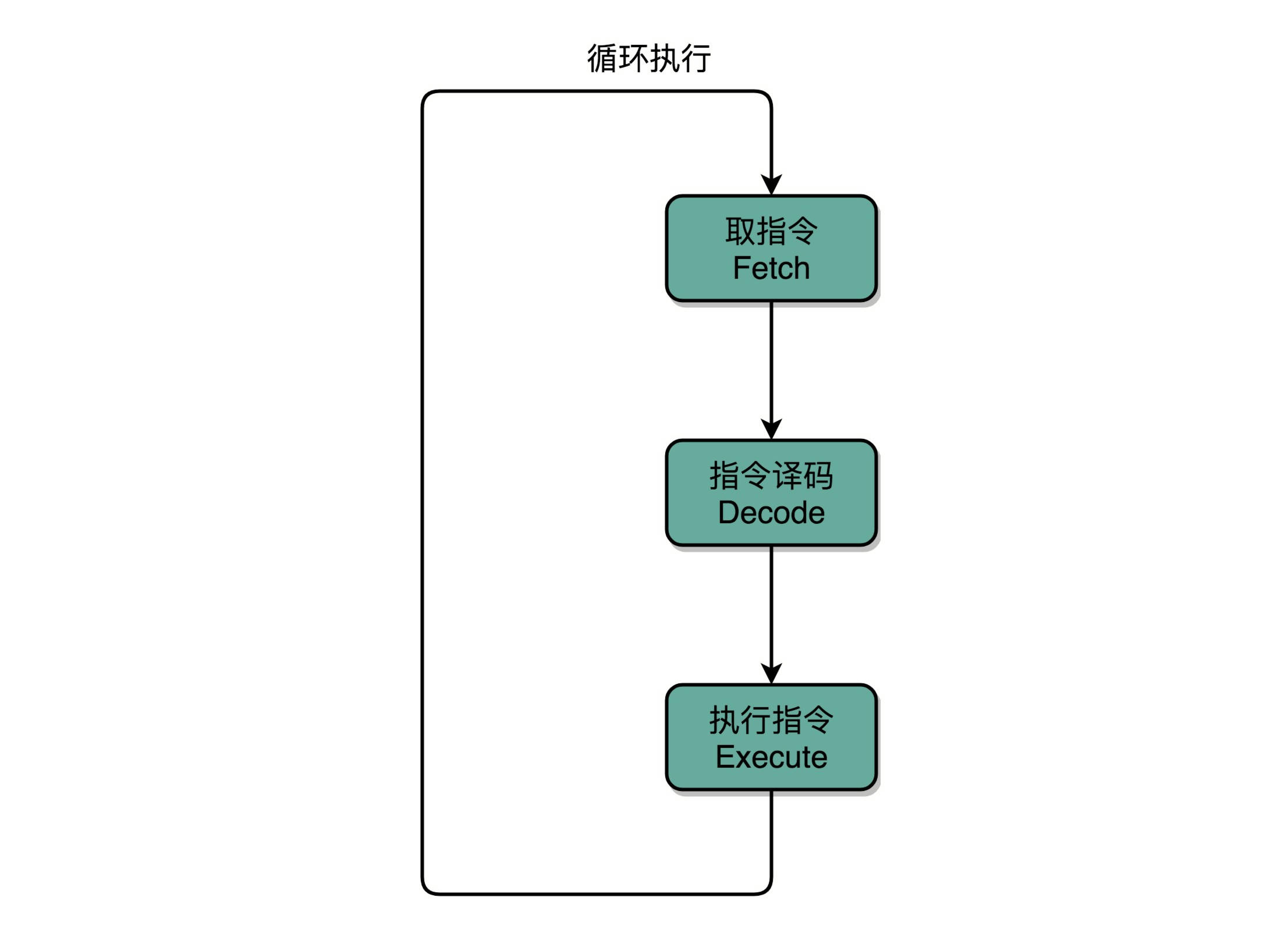

指令周期

- 执行一条指令的过程

- Fetch(取得指令)

- 从PC寄存器里面找到对应的指令地址,根据指令地址从内存里把具体的指令,加载到指令寄存器中

- 然后把PC寄存器自增,便于未来执行下一条指令

- Decode(指令译码)

- 根据指令寄存器里面的指令,解析成要进行什么样的操作,是R、I、J中的哪一种指令

- 具体要操作哪些寄存器、数据或者内存地址

- Execute(执行指令)

- 实际运行对应的R、I、J这些特定的指令,进行算术逻辑操作、数据传输或者直接的地址跳转

- 重复上面步骤

- Fetch(取得指令)

- 指令周期(Instruction Cycle):Fetch -> Decode -> Execute

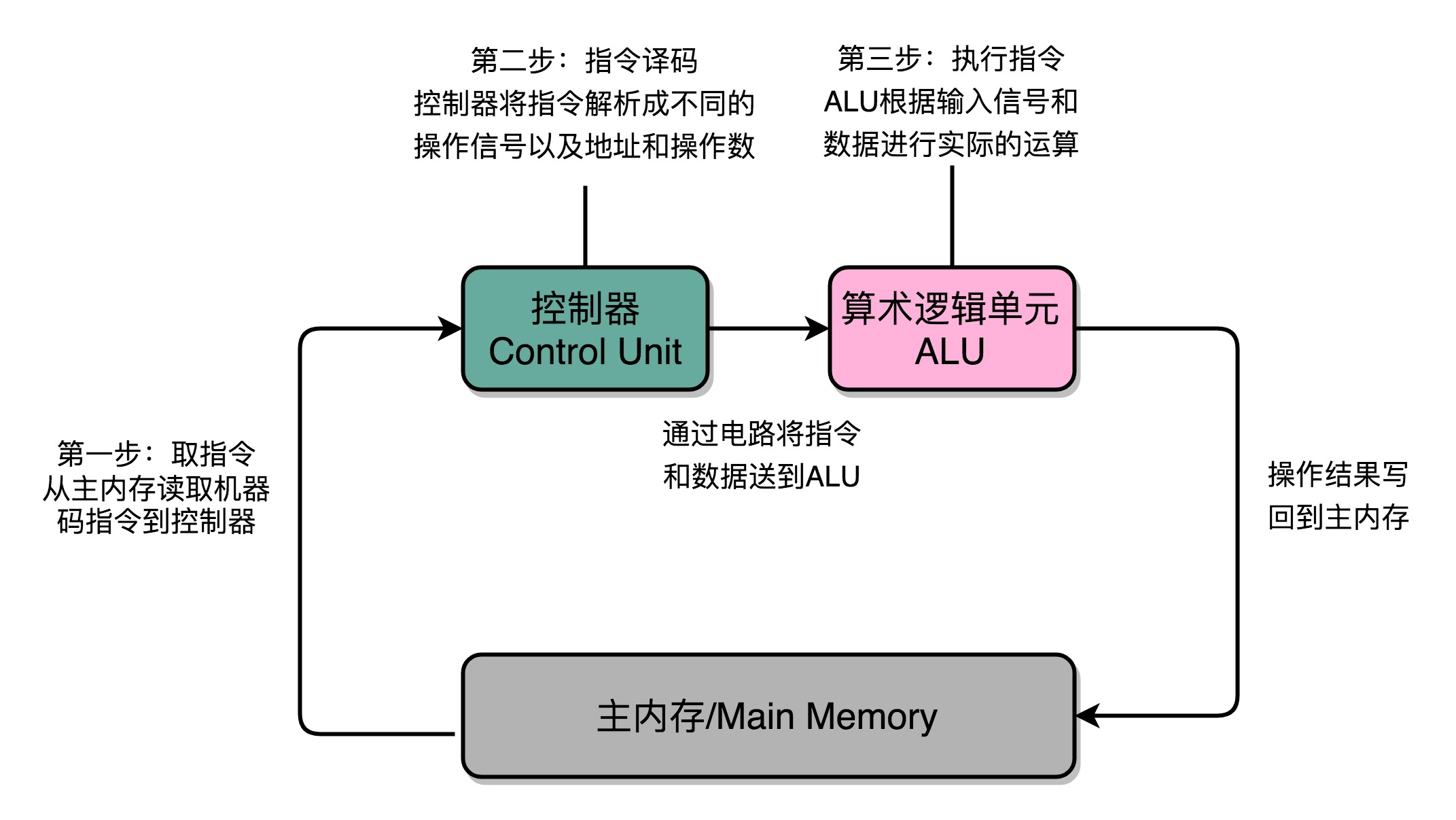

涉及的组件

- 取指令的阶段,指令是放在存储器里的

- 通过PC寄存器和指令寄存器取出指令的过程,是由控制器(Control Unit)操作的

- 指令的解码过程,也是由控制器进行的

- 一旦到了执行指令阶段,R、I型指令都是由算术逻辑单元(ALU)操作

- 进行算术操作、逻辑操作的R型指令

- 进行数据传输、条件分支的I型指令

- 如果是简单的无条件地址跳转,可以直接在控制器里面完成,不需要用到运算器

机器周期

- Machine Cycle:机器周期或者CPU周期

- CPU内部的操作速度很快,但访问内存的速度却慢很多,每条指令都需要从内存里面加载而来

- 一般把从内存里读取一条指令的最短时间,称为CPU周期

时钟周期

- Clock Cycle:时钟周期(主频)

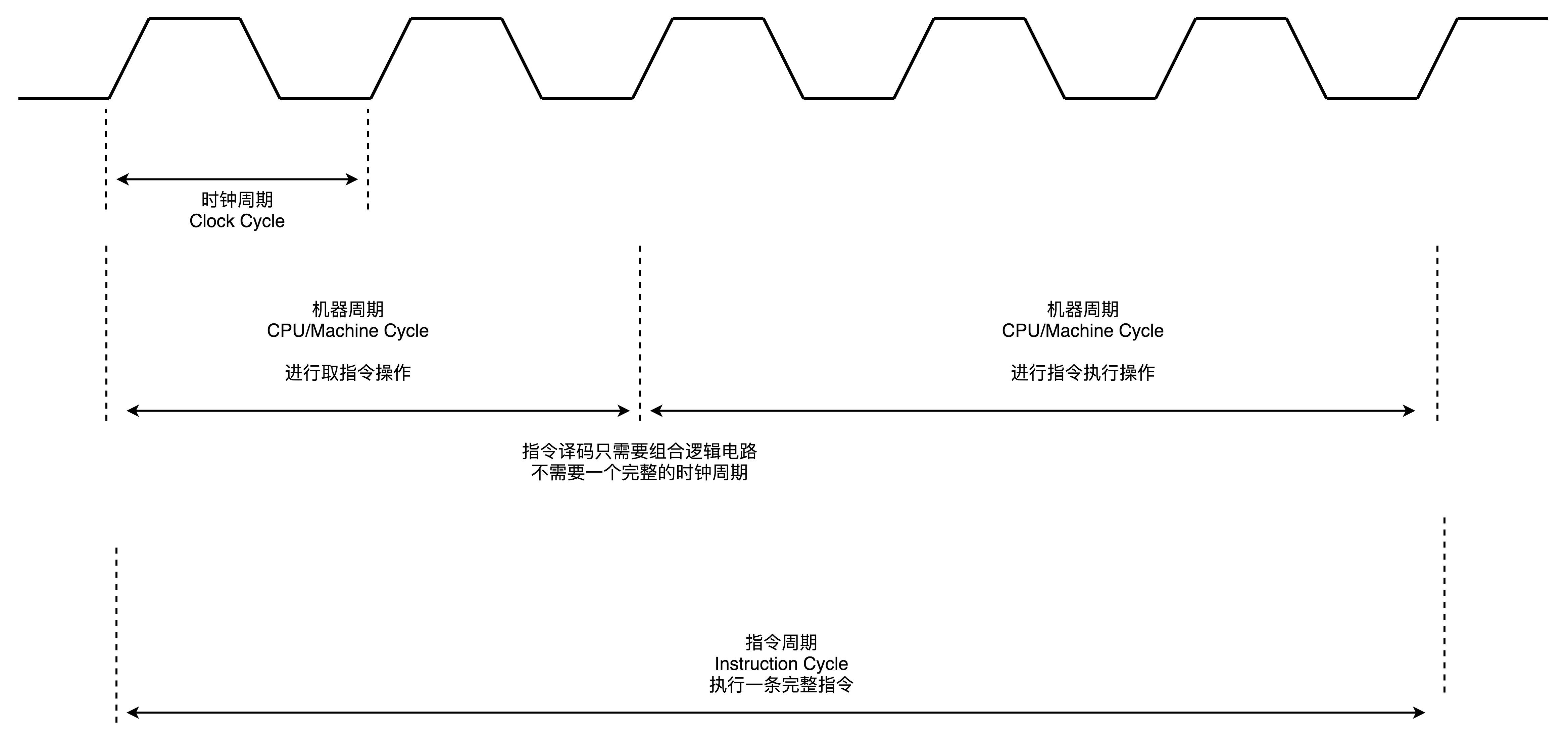

三者关系

- 一个CPU周期(机器周期),通常会由几个时钟周期累积起来

- 对于一个指令周期来说,取出一条指令,然后执行它,至少需要两个CPU周期

- 取出指令至少需要一个CPU周期,执行指令至少也需要一个CPU周期

- 指令译码只需要组合逻辑电路,不需要一个完整的时钟周期 – 时间很短

- 复杂的指令规则需要更多的CPU周期

- 取出指令至少需要一个CPU周期,执行指令至少也需要一个CPU周期

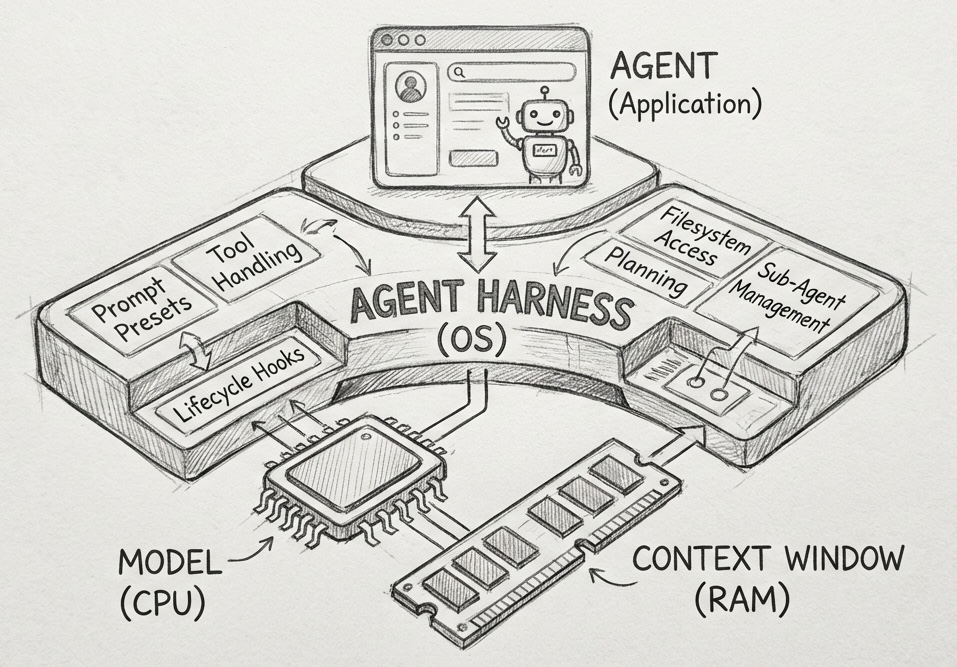

建立数据通路

- 数据通路就是处理器单元,由两类元件组成:操作元件、存储元件

- 操作元件

- 也称为组合逻辑元件,即ALU

- 功能:在特定的输入下,根据组合电路的逻辑,生成特定的输出

- 存储元件

- 也叫状态元件,如计算过程中用到的寄存器,不论是通用寄存器还是状态寄存器,都是存储元件

- 通过数据总线的方式,把操作元件和存储元件连接起来,就可以完成数据的存储、处理和传输了,建立了数据通路

控制器

- 控制器只是机械地重复Fetch -> Decode -> Execute循环中的前两个步骤

- 然后把在最后一个步骤通过控制器产生的控制信号,交给ALU去处理

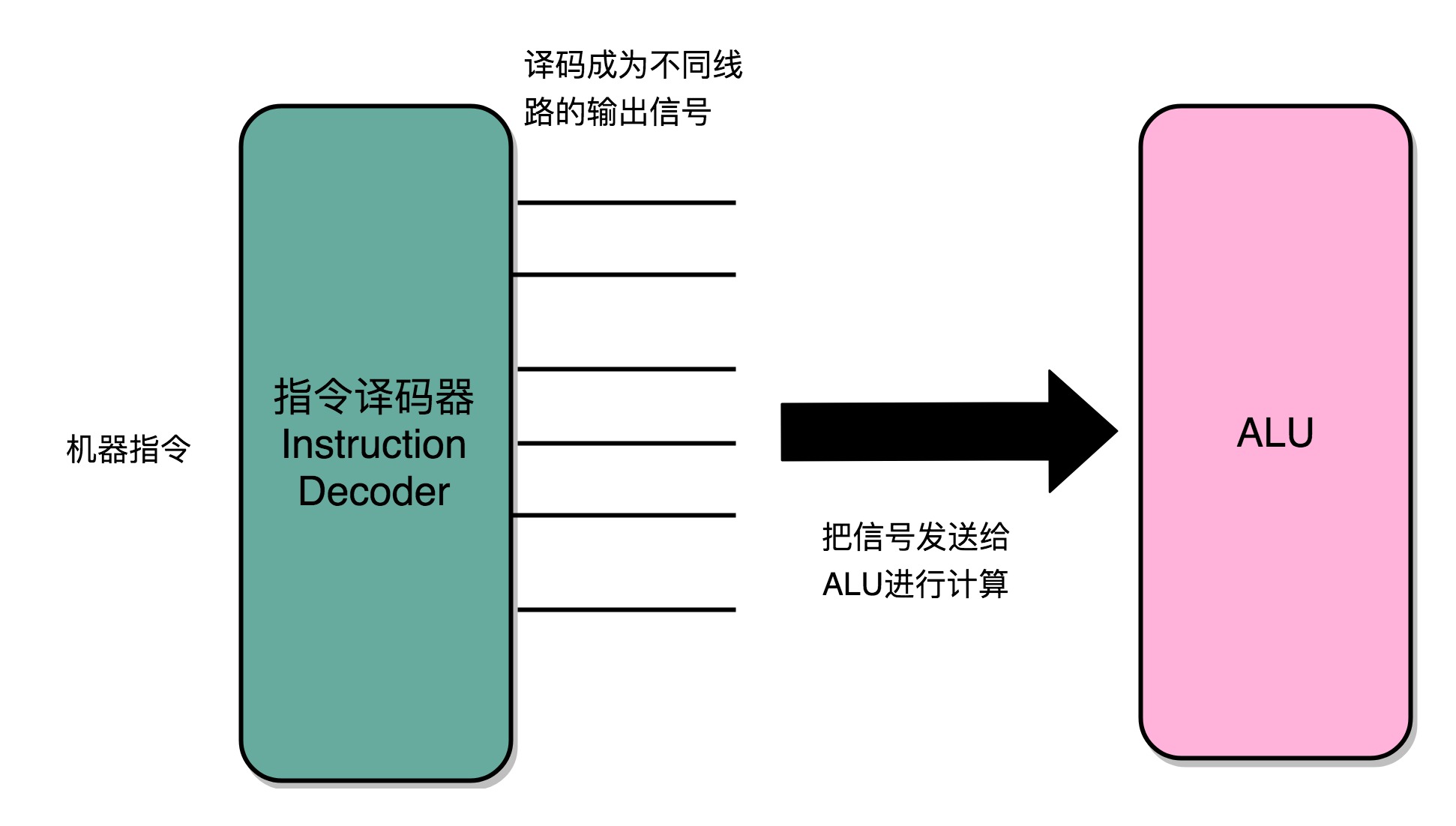

- 所有CPU支持的指令,都会在控制器里面,被解析成不同的输出信号 – 电路非常复杂

- 运算器里的ALU和各种组合逻辑电路,可以认为是一个固定功能的电路

- 控制器翻译出来的就是不同的控制信号

- 这些控制信号,告诉ALU去做不同的计算

- 指令译码器将输入的机器码(机器指令),解析成不同的操作码和操作数,然后传输给ALU进行计算

所需硬件电路

- ALU

- 一个没有状态的,根据输入计算输出的组合逻辑电路

- 寄存器

- 一个能进行状态读写的电路元件

- 这个电路能够存储上一次的计算结果

- 常见实现:锁存器(Latch)、D触发器(Data/Delay Flip-flop)

- 『自动』的电路

- 按照固定的周期,不停地实现PC寄存器自增,自动去执行Fetch -> Decode -> Execute的步骤

- PC寄存器 = 程序计数器

- 『译码』的电路

- 对指令进行decode

- 拿到内存地址去获取对应的数据或者指令

时序逻辑电路

- 组合逻辑电路:只需要给定输入,就能得到固定的输出

- 时序逻辑电路解决的问题

- 自动运行

- 时序电路接通之后可以不停地开启和关闭开关,进入一个自动运行的状态

- 场景:控制器不停地让PC寄存器自增读取下一条指令

- 存储

- 通过时序电路实现的触发器,能把计算结果存储在特定的电路里面

- 不像组合逻辑电路那样,一旦输入有任何变化,对应的输出也会改变

- 本质上解决了各个功能按照时序协调的问题

- 无论是程序实现的软件指令,还是硬件层面的各种指令操作,都有先后的顺序要求

- 时序电路使得不同的事件按照时间顺序发生

- 自动运行

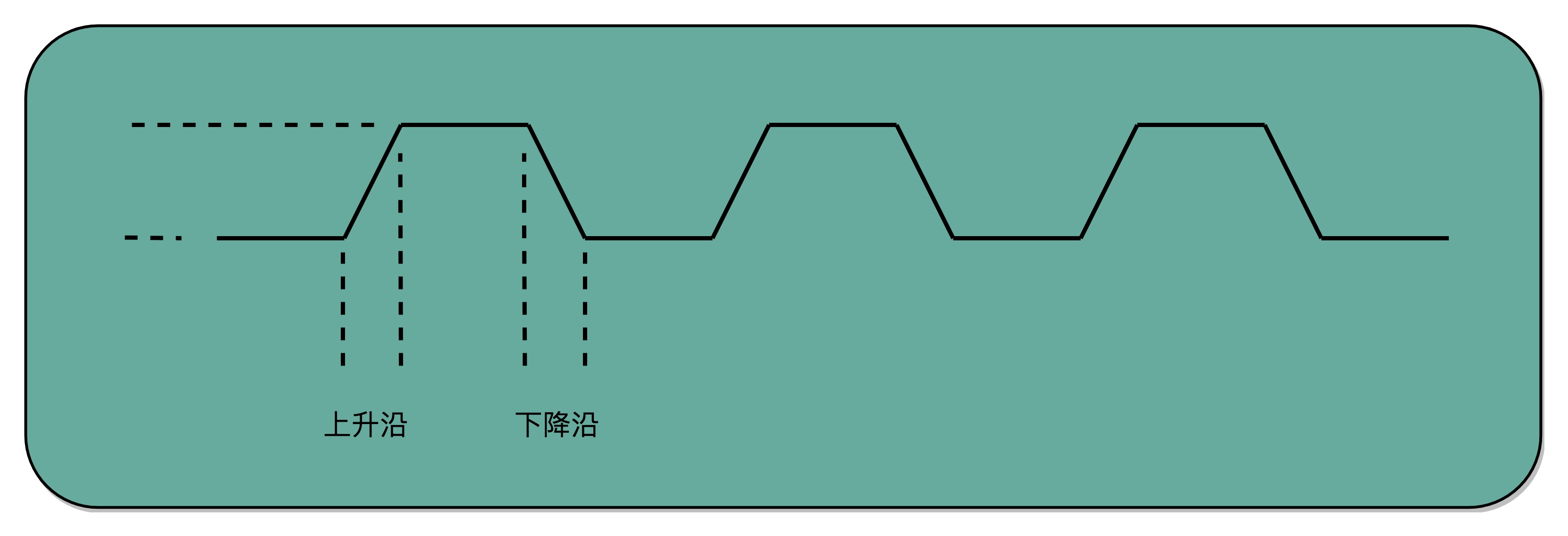

时钟信号

- CPU的主频是由一个晶体振荡器来实现的,而这个晶体振荡器生成的电路信号,就是时钟信号

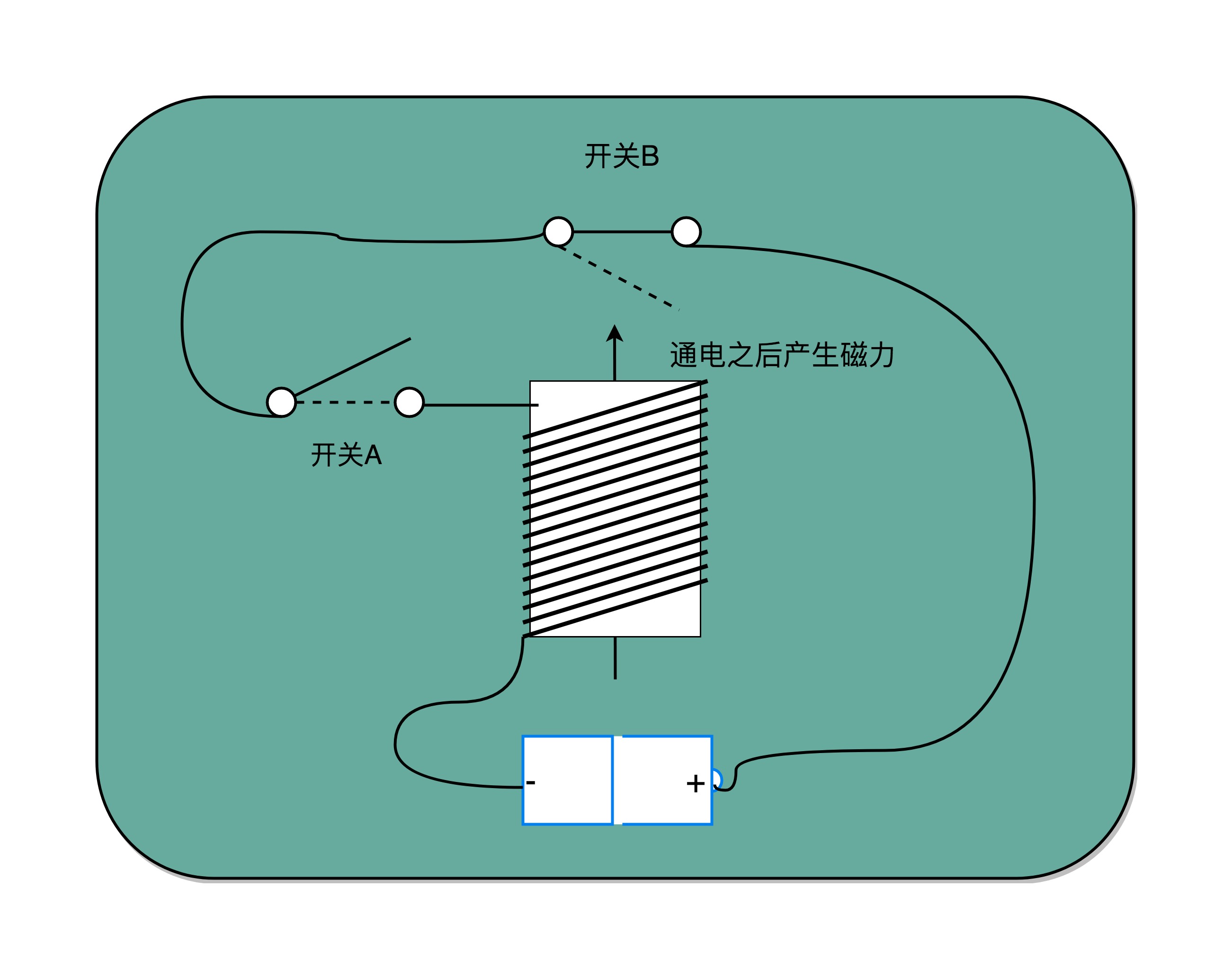

- 开关A,一开始是断开的,由手工控制;另一个开关B,一开始是合上的;磁性线圈对准开关B

- 一旦合上开关A,磁性线圈会通电,产生磁性,开关B就会从合上变成断开

- 一旦开关B断开,电路中断,磁性线圈失去磁性,于是开关B又会弹回到合上的状态

- 这样,电路就会来回不断地在开启、关闭两个状态中切换,对下游电路来说,就不断地产生0和1的信号

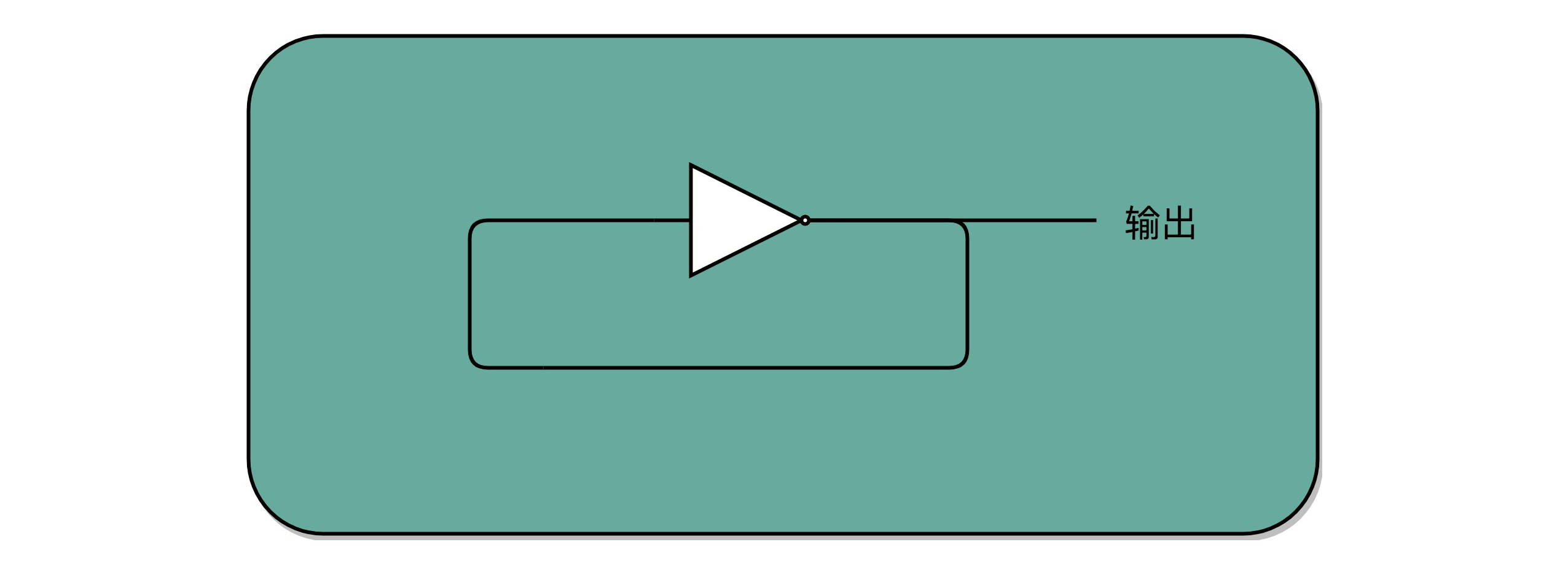

- 这种按照固定周期不断在0和1之间切换的信号,就是时钟信号(Clock Signal)

- 反馈电路:_把电路的输出信号作为输入信号,在回到当前电路_

- 通过反相器(Inverter)实现的时钟信号

D触发器 – 存储

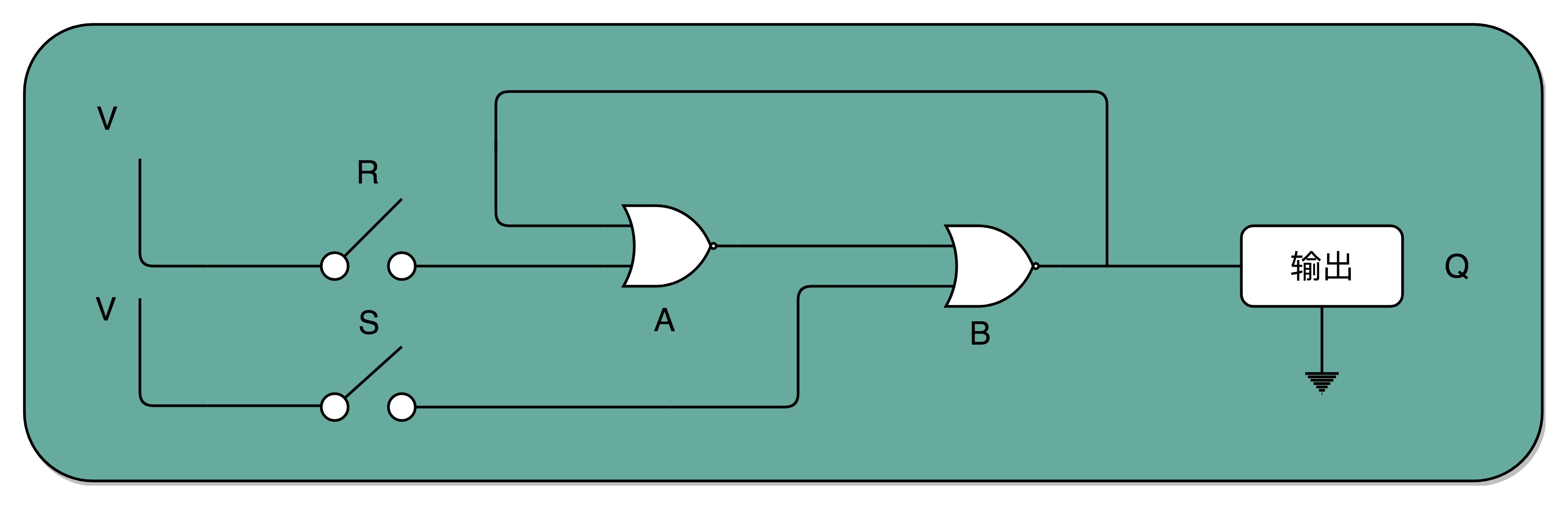

RS触发器

或非门

| NOR | 0 | 1 |

|---|---|---|

| 0 | 1 | 0 |

| 1 | 0 | 0 |

过程

- 电路一开始,输入开关都是关闭的

- A的输入:<0,0>,A的输出:1

- B的输入:<1,0>,B的输出:0,反馈到A,没有任何变化,Q的输出:0

- 把A的开关R合上

- A的输入:<0,1>,A的输出:0

- B的输入:<0,0>,B的输出:1,反馈到A,Q的输出:1

- A的输入:<1,1>,A的输出:0

- 电路仍然是稳定的,不会像晶振那样震荡

- 把A的开关R打开

- A的输入:<1,0>,A的输出:0

- B的输入:<0,0>,B的输出:1,反馈到A,Q的输出:1

- 电路依然是稳定的,开关R、S的状态和第一步是一样的,但Q的输出是1(保留上一步的输出)

- 把B的开关S合上

- B的输入:<?,1>,B的输出:0,Q的输出:0

- 小结

- 接通开关R,输出变为1,即使断开开关,输出还是1;接通开始S,输出变为0,即使断开开关,输出还是0

- 当两个开关都断开的时候,最终的输出结果,取决于之前动作的输出结果 – 记忆功能

- RS触发器也称为复位置位触发器(Reset-Set Flip Flop)

| R | S | Q |

|---|---|---|

| 1 | 0 | 1 |

| 0 | 1 | 0 |

| 0 | 0 | Q |

| 1 | 1 | NA |

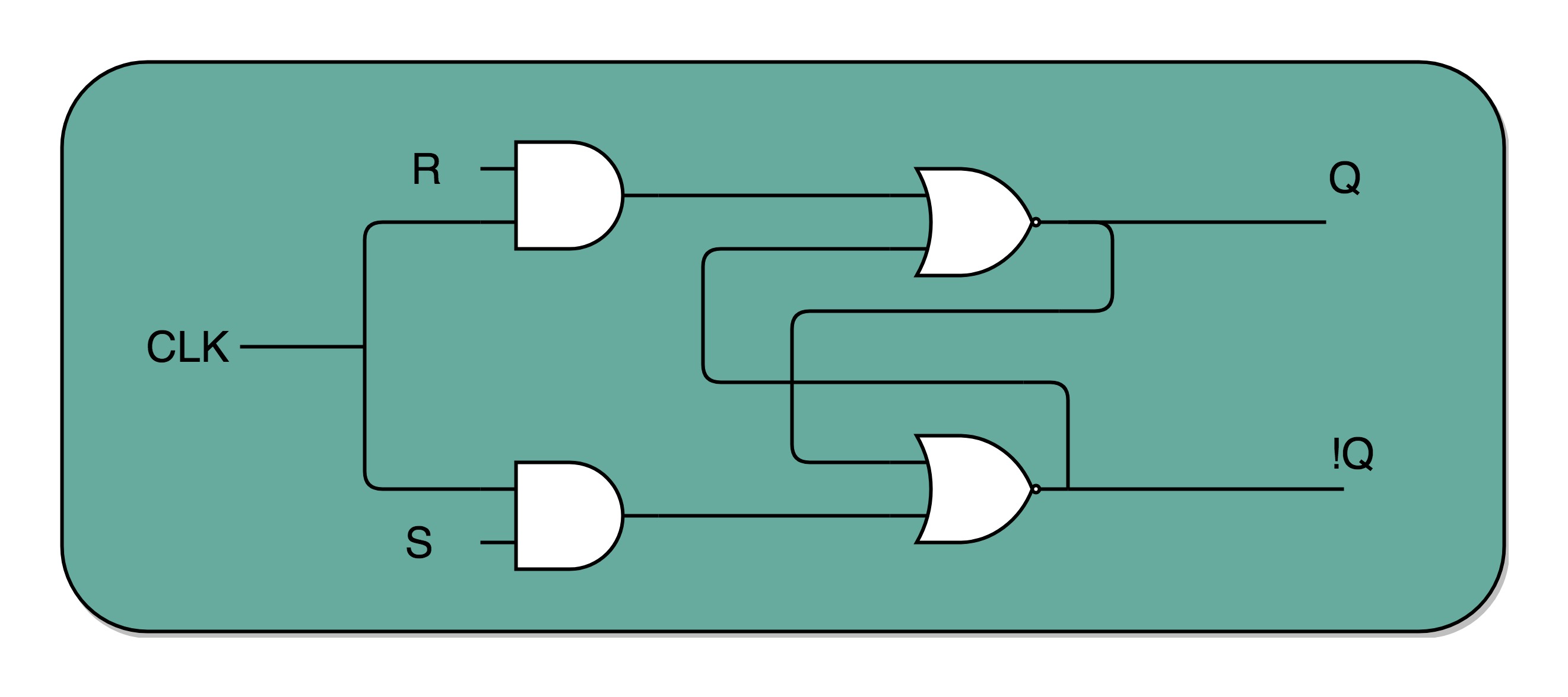

D触发器

控制何时往Q写入数据

- 在RS触发器的基础上,在R和S开关之后,加入两个与门,同时给这两个与门加入一个时钟信号CLK作为电路输入

- 当时钟信号CLK在低电平的时候,与门的输入里有一个0,两个实际的R和S后的与门的输出必然为0

- 无论怎么按R和S开关,根据R-S触发器的真值表,对应的Q值都不会发生变化

- 当时钟信号CLK在高电平的时候,与门的一个输入为1,输出结果完全取决于R和S的开关

- 此时可以通过开关R和S,来决定对应Q的输出

- 小结

- 通过一个时钟信号,可以在特定的时间对输出Q进行写入操作

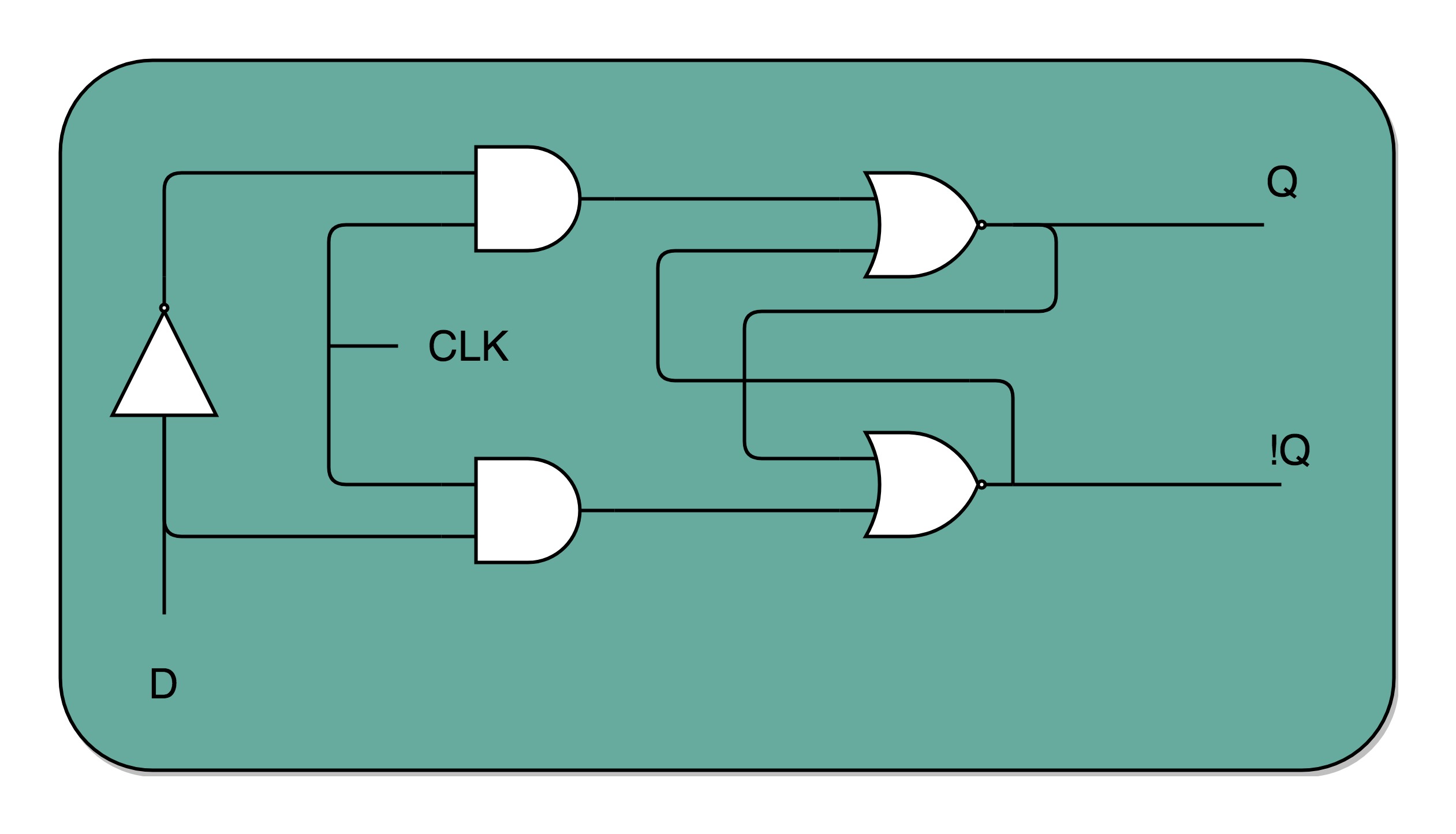

D触发器

- 让R和S的开关,通过一个反相器连起来,就是通过同一个开关控制R和S

- 当CLK信号是1,R和S就可以设置输出Q;当CLK信号是0,无论R和S怎么设置,输出信号都不会改变

- 用来控制R和S两个开关的信号,视为一个输入的数据信号,即Data,这就是D型触发器的由来

- 小结:把R和S两个信号通过一个反相器合并,可以通过一个数据信号进行Q的写入操作

- 一个D触发器,只能控制1bit的读写

- 如果同时拿出多个D触发器并列在一起,并且把用同一个CLK信号控制所有D触发器的开关

- 这样就变成了N位的D触发器,可以同时控制N位的读写

- CPU里的寄存器可以直接通过D触发器来构造的

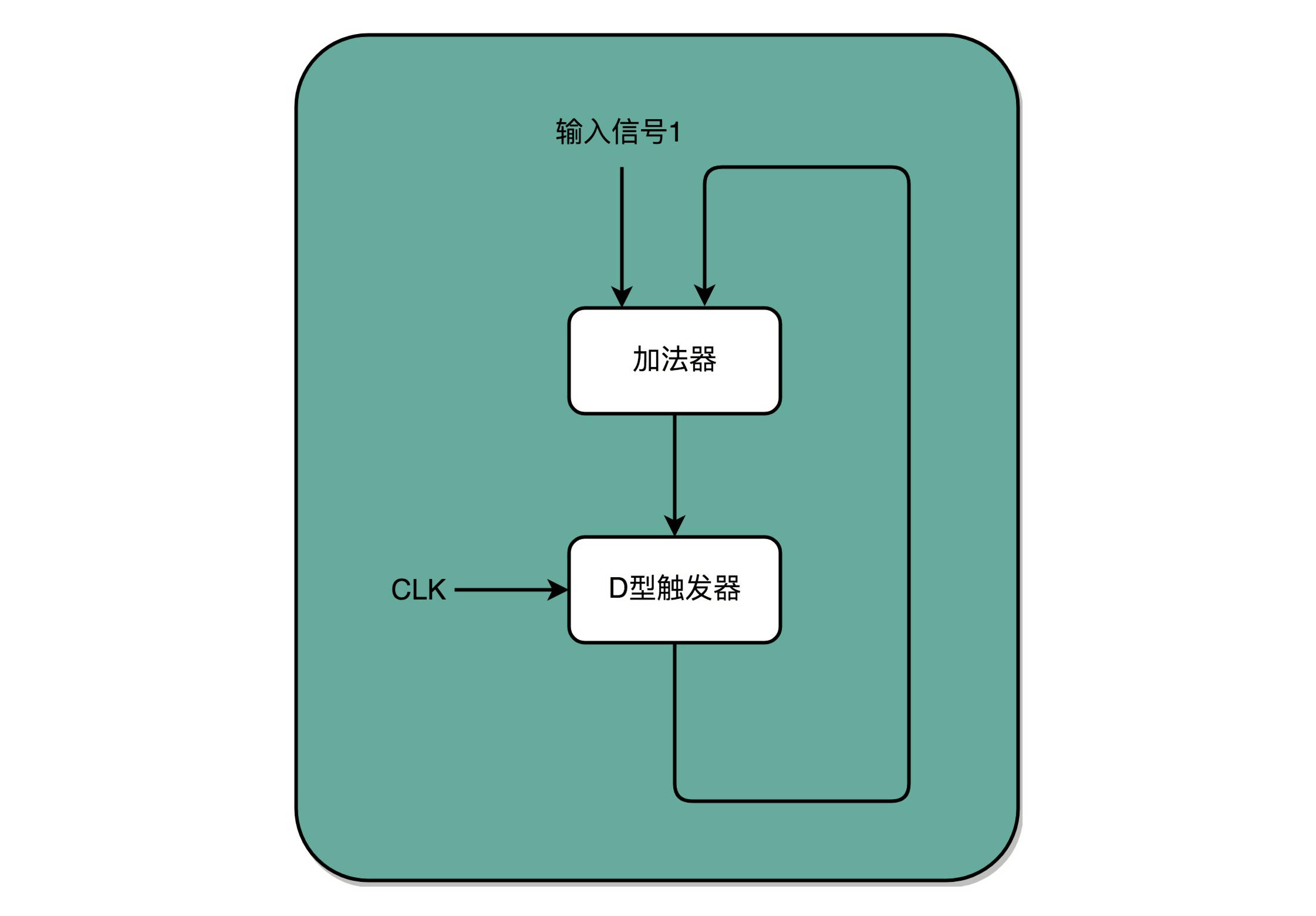

PC寄存器

- PC寄存器,也称为程序计数器(Program Counter)

- 有了时钟信号,可以提供定时的输入,有了D触发器,可以在时钟信号控制的时间点写入数据

- 把两者组合起来,就可以实现一个自动的计数器

- 加法器的两个输入,一个始终设置为1,另外一个来自于一个D触发器,把加法器的输出结果,写到D触发器

- 这样D触发器里面的数据会在固定的时钟信号为1的时候更新一次,每过一个时钟周期,就能固定自增1

- 每次自增之后,可以去对应的D触发器里取值,即下一条需要运行指令的地址(同一程序的指令要顺序存放在内存里)

- 因此同一程序顺序地存放指令,就是为了通过程序计数器就能定时不断地执行新指令

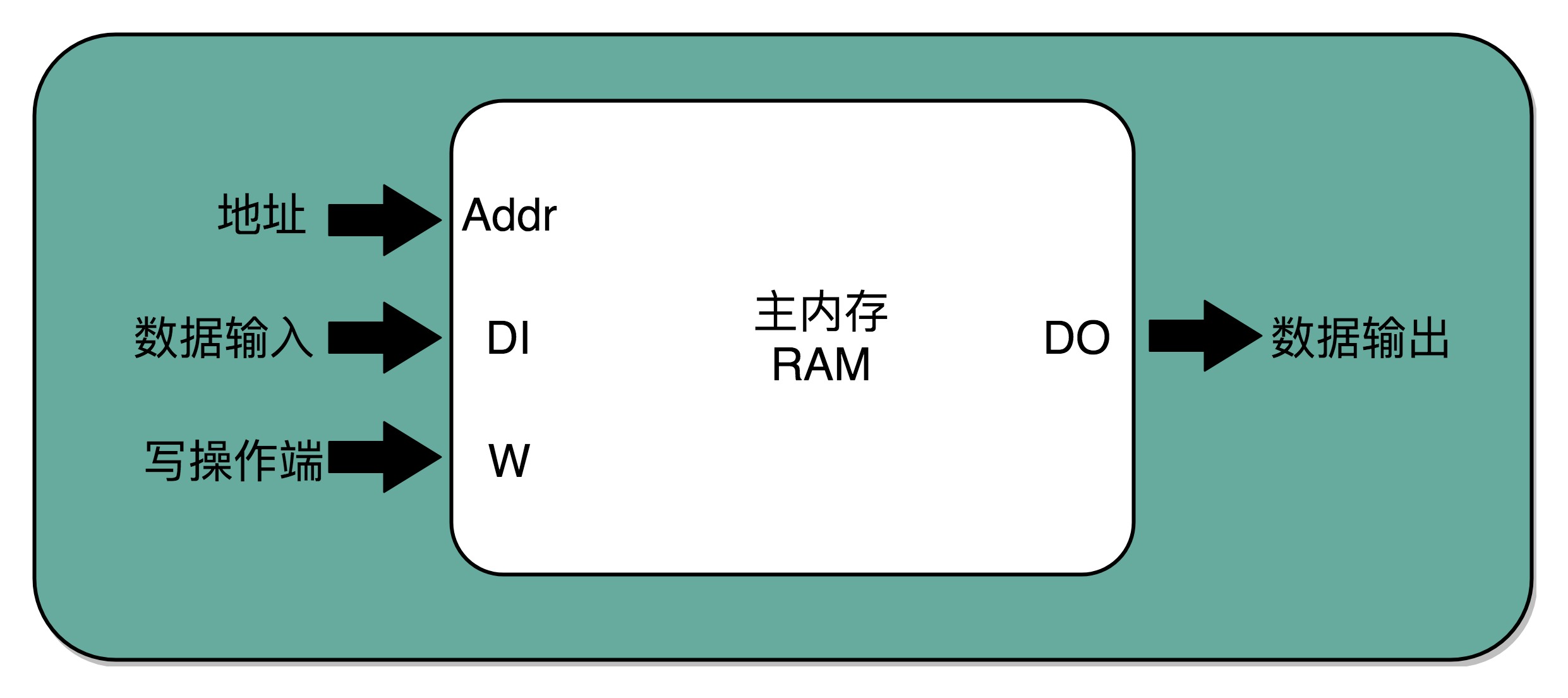

译码器

- 数据能存储在D触发器里,把很多D触发器放在一起,就能形成一块很大的存储空间,甚至当成一块内存来使用

- 在写入和读取数据时,怎么定位是操作哪一个Bit? – 寻址、译码器

- 实际使用的计算机内存使用的是DRAM,并非通过D触发器来实现的,而是使用CMOS芯片来实现 – 但不影响理解译码器的原理

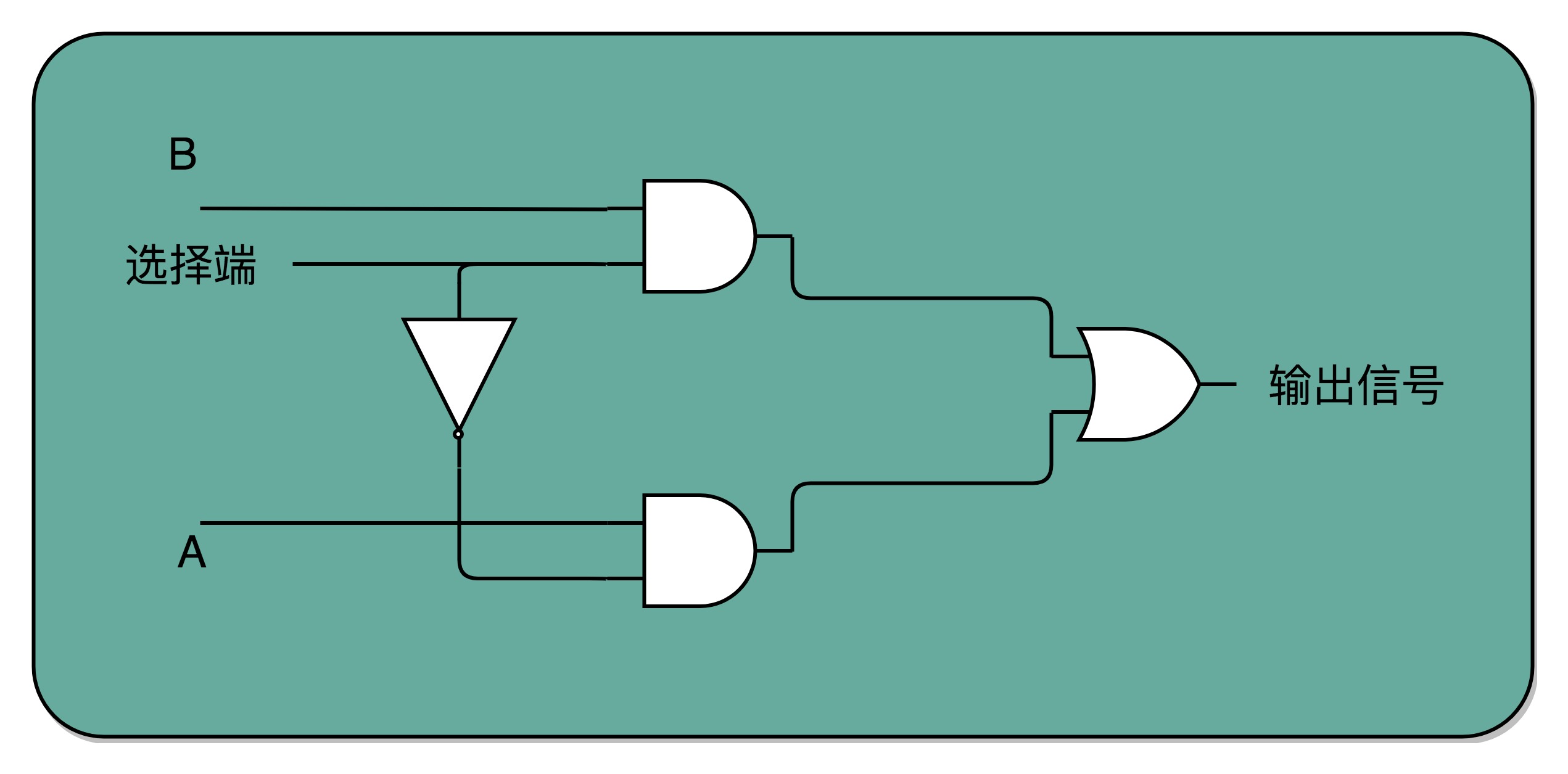

2-1选择器

- 把寻址退化到最简单的情况:在两个地址中,去选择一个地址,即2-1选择器

- 2-1选择器的组成:一个反相器、两个与门、一个或门

- 通过控制反相器的输入是0还是1,来决定对应的输出信号,是和地址A还是地址B的输入信号一致

- 一个反相器只能有0和1两种状态,所以只能从两个地址中选择一个,如果输入的信号有三个不同的开关,称为3-8译码器

- 现代计算器的CPU是64位,意味着寻址空间为**$2^{64}$,需要一个有64个开关的译码器**

本质

- 译码器的本质,是从输入的多个位的信号中,根据一定的开关和电路组合,选择出自己想要的信号

- 除了寻址外,还可以通过译码器,找出期望执行的指令,即opcode,以及后面对应的操作数或寄存器地址

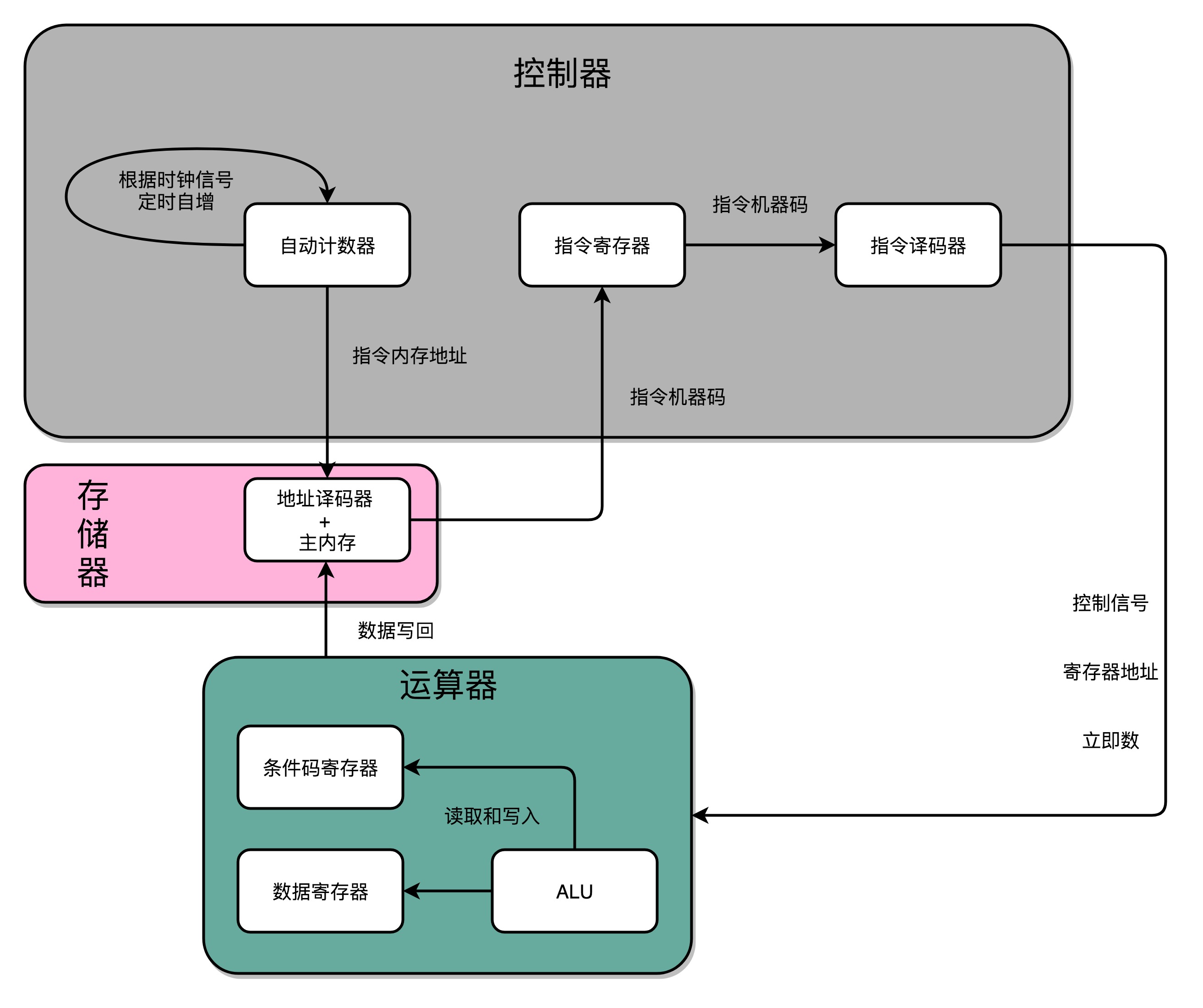

简单的CPU

- 自动计数器

- 自动计数器会随着时钟主频不断地自增,作为PC寄存器

- 地址译码器

- 地址译码器需要连着通过大量的D触发器组成的内存

- 自动计数器随着时钟主频不断自增,从地址译码器当中,找到对应的计数器所表示的内存地址,然后读取出里面的CPU指令

- 读取出来的CPU指令会通过CPU时钟的控制,写入到一个由D触发器组成的寄存器,即指令寄存器

- 指令译码器

- 指令译码器不是用来寻址的,而是将拿到的指令,解析成opcode和对应的操作数

- 拿到对应的opcode和操作数,对应的输出线路要连接ALU,开始进行各种算术和逻辑运算

- 对应的计算结果,再写回到D触发器组成的寄存器或者内存中

参考资料

All articles on this blog are licensed under CC BY-NC-SA 4.0 unless otherwise stated.