计算机组成 -- CISC + RISC

历史

- 在早期,所有的CPU都是CISC

- 实际的计算机设计和制造会严格受到硬件层面的限制,当时的计算很慢,存储空间很小

- 为了让计算机能够尽量多地工作,每个字节乃至每个比特都特别重要

- CPU指令集的设计,需要仔细考虑硬件限制,为了性能考虑,很多功能都直接通过硬件电路来完成

- 为了少用内存,指令长度也是可变的

- 常用的指令要短一些,不常用的指令要长一些

- 用尽量少的内存空间,存储尽量多的指令

- 计算机的性能越来越好,存储的空间也越来越大,70年代末,RISC出现

- CPU运行程序,80%的运行代码都在使用20%的简单指令

对比

| CISC | RISC |

|---|---|

| 以硬件为中心的指令集设计 | 以软件为中心的指令集设计 |

| 通过硬件实现各类程序指令 | 通过编译器实现简单指令组合,完成复杂功能 |

| 更高效地使用内存和寄存器 – 一开始都是CISC,硬件资源非常珍贵 | 需要更大的内存和寄存器,并更频繁地使用 |

| 可变的指令集,支持更复杂的指令长度 | 简单、定长的指令 |

| 大量指令数 | 少量指令数 |

- CISC的缺点

- 在硬件层面,如果想要支持更多的复杂指令,CPU里面的电路就要更复杂,设计起来更困难

- 更复杂的电路,在散热和功耗层面,也会面临更大的挑战

- 在软件层面,支持更多的复杂指令,编译器的优化变得更困难

- 在RISC架构里面,CPU选择把指令精简到20%的简单指令,原先复杂指令,通过简单指令组合来实现,让软件实现硬件的功能

- 这样,CPU的整个硬件设计变得简单,在硬件层面提升性能变得更加容易

- RISC的CPU里完成指令的电路变简单了,可以腾出更多空间来存放通用寄存器

- 因为RISC完成同样的功能,执行的指令数要比CISC多

- 如果需要反复从内存里面读取指令或者数据到寄存器,那么很多时间都会花在访问内存上

- 所以,RISC架构的CPU往往会有更多的通用寄存器

- RISC的CPU也可以把更多的晶体管,用来实现更好的分支预测等优化功能,进一步提升CPU实际的执行效率

- 程序的CPU执行时间 = 指令数 × CPI × Clock Cycle Time

- CISC架构,是通过优化指令数,来减少CPU的执行时间

- RISC架构,是通过优化CPI,来减少CPU的执行时间

- 因为指令比较简单,需要的时钟周期就比较少

- 因为RISC降低了CPU硬件的设计和开发难度

- 从80年代开始,大部分新的CPU都开始采用RISC架构,如IBM的PowerPC、SUN的SPARC

微指令架构

- x86架构所面临的种种问题,都来自于一个最重要的考量,即指令集的向前兼容性

- x86在商业上太成功,所以市场上有大量的Intel CPU,围绕这些CPU,又有大量系统软件(如操作系统、编译器)

- 这些系统软件只支持x86的指令集,在这些系统软件上,又有各种各样的应用软件

- 如果Intel要放弃x86的架构和指令集,开发一个RISC架构的CPU,面临的第一个问题:所有的软件都是不兼容的

- 安腾处理器:Intel想要在CPU进入64位时代的时候,丢掉x86的历史包袱,推出了全新的IA-64架构

- 但因为不兼容x86的指令集,遭遇了重大的失败

- AMD,在Intel研发安腾的时候,推出了兼容32位x86指令集的64位架构,即AMD64

- x86下的64位指令集x86-64,并不是Intel发明的,而是AMD

- Intel在开发安腾处理器的同时,也在不断地借鉴其它RISC处理器的设计思想

- 核心问题:始终向前兼容x86的指令集

- 思路:在不修改指令集的情况下,让CISC风格的指令集,用RISC的形式在CPU里面运行

- 在Pentium Pro时代,Intel开始在处理器里引入微指令架构(Micro-Instructions/Micro-Ops)

- 核心问题:始终向前兼容x86的指令集

- 在微指令架构的CPU里面,编译器编译出来的机器码和汇编代码并没有发生什么变化

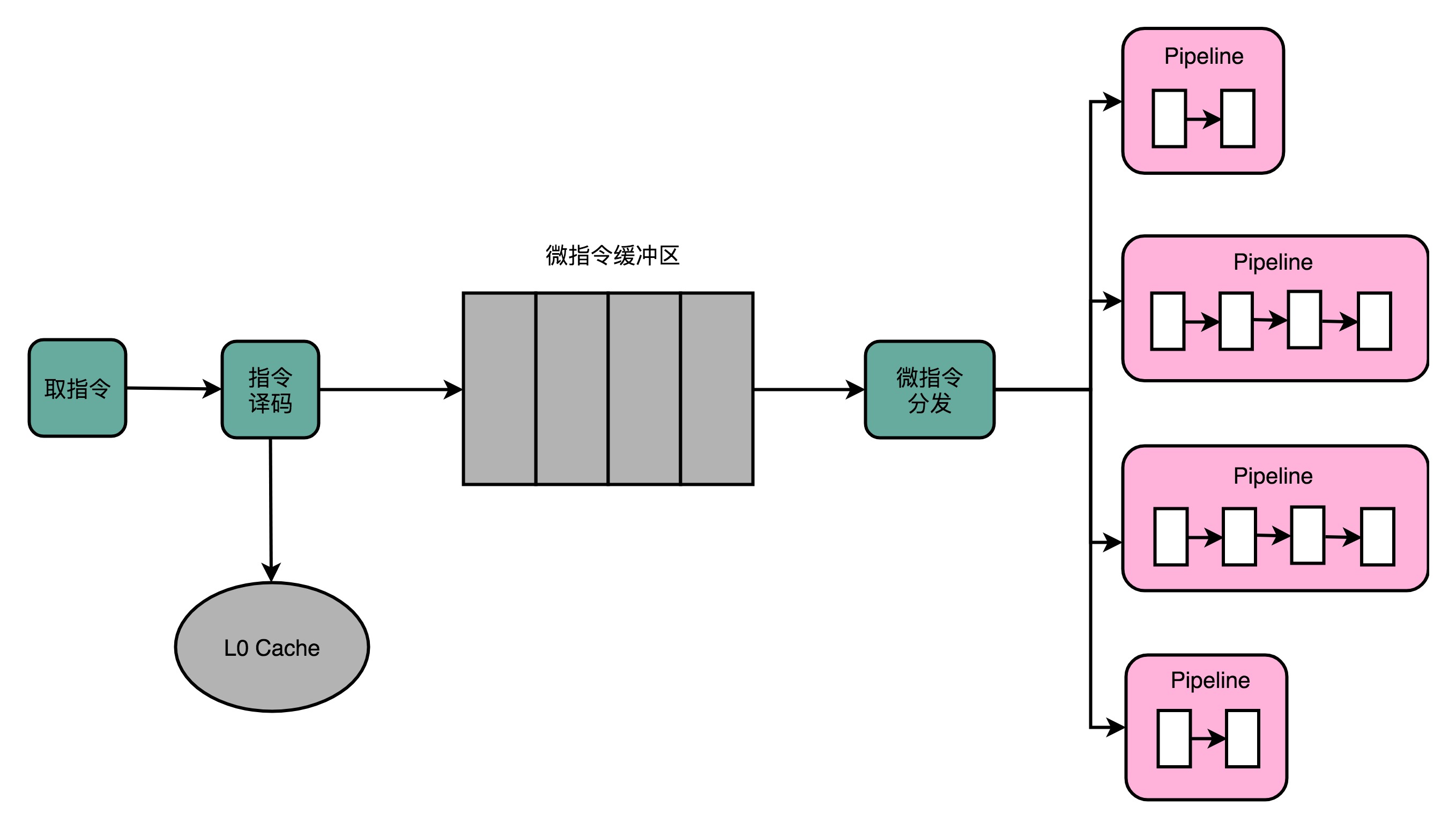

- 但在指令译码阶段,指令译码器翻译出来的,不再是某一条CPU指令,指令译码器会把一条机器码,翻译成多条微指令

- 微指令不再是CISC风格,而是变成了固定长度的RISC风格,这些RISC风格的微指令,会被放到一个微指令缓冲区里

- 然后再从微指令缓冲区里面,分发到后面的超标量并且是乱序执行的流水线架构

- 这个流水线架构接受的不是复杂的指令,而是精简的指令

- 在微指令架构里,指令译码器相当于一个适配器

- 这个适配器,填平了CISC和RISC之间的指令差异

- 但这样的指令译码器更复杂:需要把CISC指令译码成RISC指令,意味着更复杂的电路和更长的译码时间

- 本来通过RISC提升的性能,又有一部分浪费在指令译码上

- RISC优于CISC是基于一个假设:程序实际运行过程中,80%运行的代码使用20%的常用指令

- 这意味着CPU里执行的指令有很强的局部性,对于很强局部性的问题,常见的解决方案是使用缓存

- 因此,Intel在CPU里面加了一层L0 Cache,保存的是指令译码器把CISC指令翻译成RISC微指令的结果

- 在大部分情况下, CPU都可以从L0 Cache里面直接拿到译码结果,而不需要让译码器去进行实际的译码操作

- 好处:优化性能 + 减少功耗

- 从Pentium Pro开始,Intel处理器不再是一个纯粹的CISC处理器了,同时融合了大量RISC类型的处理器设计

- 由于Intel本身在CPU层面做了大量的优化(乱序执行、分支预测等),x86的CPU在功耗上始终远远超过RISC架构的ARM

ARM

- ARM:Advanced RISC Machines

- 现在的CISC和RISC的分界已经比较模糊

- Intel和AMD的CPU,都是采用译码成RISC风格的微指令来运行的

- ARM的芯片,一条指令同样需要多个时钟周期,也有乱序执行和多发射

- ARM在移动端战胜Intel的原因

- 功耗优先的设计

- 在移动设备上,功耗是一个远比性能更重要的指标

- ARM的CPU,主频更低,晶体管更少,高速缓存更小,乱序执行的能力更弱,这些都是为了功耗所做的妥协

- 低价

- ARM只进行CPU设计,然后把对应的知识产权授权出去,让其它厂商来生产ARM架构的CPU

- 甚至允许厂商(苹果、三星、华为)基于ARM架构和指令集,设计属于自己的CPU,ARM只收取对应的专利授权费用

- 多个厂商之间的竞争,使得ARM的芯片在市场上的价格很便宜

- 虽然ARM芯片的出货量远大于Intel,但收入和利润却比不上Intel

- 功耗优先的设计

参考资料

All articles on this blog are licensed under CC BY-NC-SA 4.0 unless otherwise stated.